# ISEDA29 International Symposium of EDA

May 9-12, 2025 😪 Hong Kong Disneyland, China

# **Conference Program**

## **TABLE OF CONTENTS**

| CONFERENCE COMMITTEE 1 |

|------------------------|

| SUPPORTER & SPONSORS   |

| CONFERENCE VENUE 4     |

| AGENDA OVERVIEW        |

| KEYNOTE SPEAKERS 11    |

| TUTORIALS 20           |

| PANELS 31              |

| SPECIAL SESSIONS 40    |

| TECHNICAL SESSIONS 47  |

| POSTER SESSION 105     |

| MEMO                   |

## WELCOME MESSAGE

#### Welcome to the 2025 International Symposium of EDA!

It is my immense pleasure to welcome you to this year's ISEDA, taking place for the first time in Hong Kong. This historic decision reflects, in part, the ISEDA Executive Committee's recognition of Hong Kong's strong commitment to advancing semiconductor technologies, where the ISEDA community will play a pivotal role. We are thrilled to have you join us for this exciting event, uniting thought leaders, innovators, and passionate individuals from around the globe.

Sponsored by IEEE and ACM, and jointly organized by EDA<sup>2</sup> and the EDA Committee of CIE, the ISEDA remains the premier venue for researchers and practitioners to share ground-breaking ideas and technological innovations in advancing cutting-edge computer-aided design techniques for microelectronics, devices, circuits, architectures, systems, and applications in this dynamic era of artificial intelligence. Here, you will encounter leading-edge R&D solutions and identify future research directions. We encourage you to engage in dynamic discussions with other attendees and explore new collaborative opportunities.

This year has set a new record for paper submissions, with 214 entries across 12 technical tracks from 7 regions and countries. To ensure a thorough review process, we invited 181 exceptional experts as our Technical Program Committee members. Accepted papers are organized into 27 technical sessions, alongside 2 special sessions and 7 embedded tutorials that provide in-depth insights from established experts. We are also hosting three panels on a range of compelling topics, such as 'AI/LLM for IC Manufacturing', 'Scaling up AI-Assisted EDA Techniques with Large Foundation AI Models', and 'The Fusion of AI and Multiphysics: Accelerating EDA Revolution'. These panels will provide an excellent opportunity for more in-depth interaction. We encourage you to participate and consider extending your stay to engage with these panels.

Keynotes are a highlight of ISEDA, and we are honoured to feature ten distinguished speakers this year. Saturday's keynote will be delivered by Dr. Giovanni De Micheli from École polytechnique fédérale de Lausanne, Dr. Georges Gielen from Katholieke Universiteit Leuven, and Dr. Hong Zhou from Huawei. On Sunday, Dr. Sung Kyu Lim from Georgia Institute of Technology, Dr. Ulf Schlichtmann from Technical University of Munich and Dr. Jinjun Xiong from University at Buffalo will deliver keynote talks. Monday's keynote will be delivered by Dr. Tim Cheng from The Hong Kong University of Science and Technology, Dr. Sachin S. Sapatnekar from the University of Minnesota, Dr. Jaijeet Roychowdhury from University of California, Berkeley and Dr. Vijay Janapa Reddi from Harvard University.

The success of ISEDA hinges on your participation. We hope you will reconnect with old friends and forge new connections. Additionally, we invite you to enjoy an exciting social event in Hong Kong Disneyland Hotel, a venue that seamlessly combines sophistication, modern amenities, and the enchanting charm of Disney. Please make the most of your time here by exploring all the incredible activities Hong Kong has to offer.

Lastly, I want to extend heartfelt gratitude to our generous sponsors, dedicated supporters, and tireless volunteers that include members of the executive committee, technical program committee, and numerous student activity organizers. Your collective efforts have made this year's ISEDA a reality. Thank you!

Looking forward to an inspiring event!

#### **Conference Chairs of ISEDA 2025**

Dr. Tsuna-Yi Ho

The Chinese University of Hong Kong

**Dr. Runsheng Wang** Peking University

**Ór. Gang Qu** University of Maryland

## **CONFERENCE COMMITTEE**

#### **EXECUTIVE COMMITTEE**

#### **General Chairs**

Yue Hao Professor of Xidian University Academician of the Chinese Academy of Sciences **Zheng You** President of Huazhong University of Science and Technology Academician of the Chinese Academy of Engineering

#### **STEERING COMMITTEE**

Shaojun Wei, Tsinghua University

Xuan Zeng, Fudan University

Patrick Girard, French National Center for Scientific

Research

Jamal Deen, McMaster University

Yankin Tanurhan, Synopsys

#### **TECHNICAL PROGRAM COMMITTEE**

Conference Chairs Tsung-Yi Ho, The Chinese University of Hong Kong Runsheng Wang, Peking University Gang Qu, University of Maryland

Technical Program Chairs Bei Yu, The Chinese University of Hong Kong Yun Liang, Peking University Ulf Schlichtmann, Technical University of Munich

Special Session Chair Wenjian Yu, Tsinghua University

Industrial Session Chair Fan Yang, Shenzhen GWX Technology Co.,Ltd.

Tutorial/Training Chair Zuochang Ye, Tsinghua University

#### **Finance Chair**

Gang Chen, Nanjing Industrial Innovation Center of EDA

Panel Chair Yibo Lin, Peking University

Publication Chair Qiang Xu, The Chinese University of Hong Kong

Industry Liaison Yutao Ma, Primarius Technologies Co.,Ltd

Publicity Chair Xin Li, Duke Kunshan University

Outreach Chair-US Hai Zhou, Northwestern University

Outreach Chair-Canada Peter Chun, University of Alberta

Outreach Chair-Europe Zebo Peng, Linköping University

Outreach Chair-Asia Xiaoqing Wen, Kyushu Institute of Technology

#### **TRACK COMMITTEE**

[1] System-Level Modeling and Design Methodology

Chair

Jieru Zhao, Shanghai Jiao Tong University

Co-Chair

Qi Sun, Zhejiang University

[2] Memory Architecture and Near/In Memory

Computing

Chair

Xiaoming Chen, Institute of Computing

Technology, CAS

Co-Chair

Li Du, Nanjing University

#### [3] Analog-Mixed Signal Design Automation

Chair Fan Yang, Fudan University Co-Chair Keren Zhu, Fudan University

# [4] High-Level, Behavioral, and Logic Synthesis and Optimization Chair Zhufei Chu, Ningbo University Co-Chair Weikang Qian, Shanghai Jiao Tong University

## [5] Analysis and Optimization for Power and TimingChairYibo Lin, Peking University

**Co-Chair Zhiyao Xie**, The Hong Kong University of Science and Technology

#### [6] Physical Implementation

Chair Hailong Yao, University of Science and Technology Beijing Co-Chair

**Yuzhe Ma**, The Hong Kong University of Science and Technology (Guangzhou)

#### [7] Testing, Validation, Simulation, and

#### Verification

#### Chair

**Huawei Li**, Institute of Computing Technology, CAS

#### **Co-Chair**

Hongce Zhang, The Hong Kong University of Science and Technology (Guangzhou)

[8] Design for Manufacturability and Reliability

Chair

Lan Chen, Institute of Microelectronics, CAS

Co-Chair

Yu-Guang Chen, National Central University

[9] Packaging & Multi-Physics Simulation

Chair

Hongliang Lu, Xidian University

Co-Chair

Yarui Peng, University of Arkansas

# [10] Technology & Modeling Chair Lining Zhang, Peking University Co-Chair Hao Yan, Southeast University

[11] Emerging Technologies and Applications

Chair

Xiangshui Miao, Huazhong University of Science and Technology

Co-Chair

Hailong You, Xidian University

# [12] Al & Open Source EDA Chair Guojie Luo, Peking University Co-Chair Xingquan Li, Peng Cheng Laboratory

## **SUPPORTER & SPONSORS**

#### **SPECIAL SUPPORTER**

https://www.hisilicon.com/cn

#### **DIAMOND SPONSORS**

https://empyrean.com.cn

https://www.semitronix.com

**GALA DINNER SPONSOR**

https://www.amedac.com

**PLATINUM SPONSORS**

https://www.univista-isg.com

https://www.primarius-tech.com

**GOLD SPONSORS**

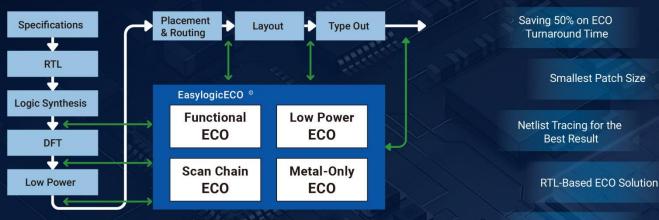

https://www.easylogiceda.com

https://www.xpeedic.com

https://www.s2ceda.com/ch

May 9-12, 2025 🐓 Hong Kong Disneyland, China

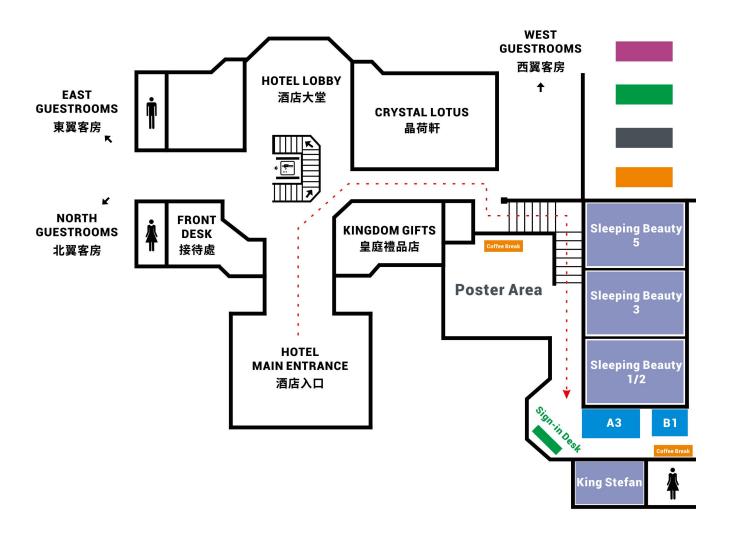

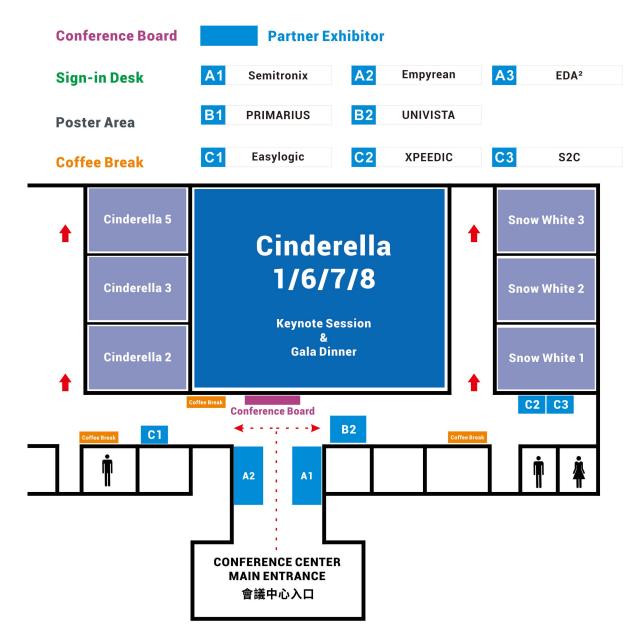

## **CONFERENCE VENUE**

### **Hong Kong Disneyland Hotel**

Address: Hong Kong Disneyland Resort, Lantau Island, Hong Kong

## **Hong Kong Disneyland Hotel**

## **AGENDA OVERVIEW**

Sign-in & Conference Materials Collection

May 09 | 11:00-20:00 May 10 | 08:00-18:00 May 11 | 08:00-16:00 May 12 | 08:00-13:00

Conference Center @ Disneyland Hotel

| May 9, 2025   Friday |                                                                                                       |                     |

|----------------------|-------------------------------------------------------------------------------------------------------|---------------------|

| 12:00-14:00          | Lunch @ Enchanted Garden Restaurant                                                                   |                     |

| 14:00-17:00          | <b>Tutorial 1</b><br>Test and Health Monitoring under Approximations and Variations                   | Snow White 1        |

|                      | Tutorial 2<br>Advanced Open-Source FPGA HLS and Physical Implementation Tools                         | Cinderella 3        |

|                      | <b>Tutorial 3</b><br>VLSI Physical Design, From 2D to 3D                                              | Cinderella 2        |

|                      | <b>Tutorial 4</b><br>AHS: An EDA toolbox for Agile Chip Front-end Design                              | Sleeping Beauty 3   |

|                      | Tutorial 5<br>Formal Verification for EDA                                                             | Sleeping Beauty 5   |

|                      | Tutorial 6<br>LLM Applications in EDA                                                                 | Sleeping Beauty 1/2 |

|                      | <b>Tutorial 7</b><br>AI-Driven Breakthroughs in Next-Generation Circuit Simulation and<br>Reliability | Snow White 2/3      |

| 15:20-15:40          | Break                                                                                                 | Foyer               |

| May 10, 2025   Saturday                                       |                                                                                                        |                     |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------|

| 08:00-08:30                                                   | Morning Coffee & Tea                                                                                   | Foyer               |

| 08:30-09:00                                                   | Opening Ceremony & Announcement of ISEDA 2026                                                          |                     |

| Keynote Speech 1 & 2<br>Host: Xin Li, Duke Kunshan University |                                                                                                        |                     |

| 09:00-09:40                                                   | <b>Prof. Giovanni De Micheli</b> , École polytechnique fédérale de Lausanne (EPFL)                     | Cinderella Ballroom |

|                                                               | Speech Title: The Future of Computing Systems Design                                                   |                     |

|                                                               | Prof. Georges Gielen, Katholieke Universiteit Leuven (KU Leuven)                                       |                     |

| 09:40-10:20                                                   | Speech Title: DeepDesignAMS: Will Tomorrow's Analog Integrated                                         |                     |

|                                                               | Circuits be Generated by AI?                                                                           |                     |

| 10:20-10:40                                                   | Break                                                                                                  | Foyer               |

|                                                               | Technical Session 1                                                                                    | Sleeping Beauty 1/2 |

|                                                               | System-Level Simulation, Modeling, and Co-Verification                                                 | bleeping beauty 1/2 |

|                                                               | Technical Session 2                                                                                    | Snow White 2/3      |

|                                                               | Innovative Simulation and Data Compression for Verification                                            | Show White 2/5      |

| 10:40-12:00                                                   | Technical Session 3                                                                                    | Sleeping Beauty 5   |

| 10.40-12.00                                                   | Emerging Transistor Technologies and Novel Process Innovations                                         | Sleeping beauty 5   |

|                                                               | Technical Session 4                                                                                    | Spow White 1        |

|                                                               | Emerging Technologies and Applications in EDA                                                          | Snow White 1        |

|                                                               | Technical Session 5                                                                                    | Sleeping Beauty 3   |

|                                                               | Large Language Models and Next-Generation EDA Tools                                                    |                     |

| 12:00-14:00                                                   | Lunch & Keynote Speech                                                                                 |                     |

| 12:30-12:40                                                   | Address from Special Guest <b>Mr. Albert Wong</b> , Hong Kong Science and Technology Parks Corporation |                     |

|                                                               | Keynote Speech 3                                                                                       | Cinderella Ballroom |

|                                                               | Host: Yu Huang, HiSilicon Technologies Co., Ltd.                                                       |                     |

|                                                               | Dr. Hong Zhou, Institute of Strategic Research, Huawei                                                 |                     |

| 12:40-13:20                                                   | Speech Title: Building a Better Connected and Intelligent World with                                   |                     |

|                                                               | STCO Collaborative Development                                                                         |                     |

|                                                               | Technical Session 6                                                                                    |                     |

|                                                               | Analog/Mixed-Signal Synthesis and Layout Optimization                                                  | Snow White 1        |

|                                                               | Technical Session 7                                                                                    |                     |

|                                                               | High-Level and Behavioral Synthesis: Trends and Optimization                                           | King Stefan         |

|                                                               | Technical Session 8                                                                                    |                     |

| 14:00-15:40                                                   | Physical Design and 3D/2.5D Integration Techniques                                                     | Sleeping Beauty 3   |

|                                                               | Technical Session 9                                                                                    |                     |

|                                                               | Reliability Engineering and Post-Layout Optimization                                                   | Snow White 2        |

|                                                               | Technical Session 10                                                                                   |                     |

|                                                               | AI-Driven Design Automation and Open Source Initiatives                                                | Sleeping Beauty 1/2 |

#### May 10, 2025 | Saturday

|             | <b>Special Session 1</b><br>CEDA-adjoint Special Session: Deep Learning Inspired Algorithms for<br>Physical Modeling and Analysis of Advanced IC Design | Snow White 3        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 14:00-15:40 | Panel 1<br>Scaling up AI-Assisted EDA Techniques with Large Foundation AI<br>Models                                                                     | Sleeping Beauty 5   |

| 15:40-16:00 | Break                                                                                                                                                   | Foyer               |

| 15:40-16:00 | Poster Session @ Poster Area of Conference Center @ Disneyland Hotel                                                                                    |                     |

|             | Technical Session 11<br>Innovations in Memory Architecture and Near/In-Memory Computing                                                                 | Snow White 3        |

| 16:00-18:00 | Technical Session 12<br>Advanced Floorplanning and Macro Placement                                                                                      | Sleeping Beauty 1/2 |

|             | <b>Technical Session 13</b><br>Design-Technology Co-Optimization and Manufacturability                                                                  | King Stefan         |

|             | <b>Technical Session 14</b><br>Efficient Parameter Extraction and Modeling Techniques                                                                   | Snow White 1        |

|             | <b>Technical Session 15</b><br>Large Language Models and Next-Generation EDA Tools                                                                      | Snow White 2        |

|             | <b>Special Session 2</b><br>Bridging AI and Hardware: Advancing Specialized Circuits, Design<br>Automation, and Manufacturing                           | Sleeping Beauty 3   |

|             | Panel 2<br>Al/LLM for IC Manufacturing                                                                                                                  | Sleeping Beauty 5   |

| 18:30-21:00 | Gala Dinner Sponsored by AMEDAC                                                                                                                         | Cinderella Ballroom |

|             | May 11, 2025   Sunday                                                                                                                                                            |                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 08:30-09:00 | Morning Coffee & Tea                                                                                                                                                             | Foyer               |

|             | Keynote Speech 4 & 5<br>Host: Tsung-Yi Ho, The Chinese University of Hong Kong                                                                                                   | Cinderella Ballroom |

| 09:00-09:40 | <b>Prof. Sung Kyu Lim</b> , Georgia Institute of Technology (Gatech)<br><b>Speech Title</b> : Enhancing AI Chip Design: AI and Traditional Algorithms for Multi-Chip Integration |                     |

| 09:40-10:20 | <b>Prof. Ulf Schlichtmann</b> , Technical University of Munich (TUM)<br><b>Speech Title</b> : Optical Networks-on-Chip: EDA for the Future of<br>Interconnect                    |                     |

| 10:20-10:40 | Break                                                                                                                                                                            | Foyer               |

|             | Technical Session 16<br>Power Modeling, Analysis, and Thermal Management                                                                                                         | Sleeping Beauty 1/2 |

| 10:40-12:00 | Technical Session 17<br>Advanced Test Methodologies and DFT Techniques                                                                                                           | Sleeping Beauty 3   |

| 10.40-12.00 | Technical Session 18Device Compact Modeling and Process Simulation                                                                                                               | Sleeping Beauty 5   |

|             | Technical Session 19<br>Emerging Technologies and Applications in EDA                                                                                                            | Snow White 2/3      |

| 12:00-14:00 | Lunch & Keynote Speech                                                                                                                                                           | Cinderella Ballroom |

|             | Keynote Speech 6<br>Host: Tsung-Yi Ho, The Chinese University of Hong Kong                                                                                                       |                     |

| 12:30-13:10 | <ul><li>Prof. Jinjun Xiong, University at Buffalo</li><li>Speech Title: A Reflection on Machine Learning for EDA: What are Possible Future Directions?</li></ul>                 |                     |

| 13:10-13:30 | Invited Talk from Ms. Qin Wang, Huawei Technologies Co., Ltd<br>Speech Title: All-Domain Collaboration: Kunpeng Computing Bedrock<br>Promotes Domestic EDA Innovation            |                     |

|             | <b>Technical Session 20</b><br>Advanced Analog Simulation and Verification Techniques                                                                                            | Sleeping Beauty 1/2 |

| 14:00-15:40 | Technical Session 21<br>Routing, Interconnect, and Partitioning Innovations                                                                                                      | Sleeping Beauty 3   |

|             | <b>Technical Session 22</b><br>Artificial Intelligence in EDA: Library, Innovation and Applications                                                                              | Sleeping Beauty 5   |

|             | Panel 3<br>The Fusion of AI and Multiphysics: Accelerating EDA Revolution                                                                                                        | Snow White 2/3      |

| 16:00       | Social Event                                                                                                                                                                     | Disneyland Park     |

#### May 9-12, 2025 🐓 Hong Kong Disneyland, China

|                                                                | Way 12, 2025   Wollday                                                         |                                         |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------|--|

| 08:30-09:00                                                    | Morning Coffee & Tea                                                           | Foyer                                   |  |

| Keynote Speech 7 & 8                                           |                                                                                |                                         |  |

|                                                                | Host: <b>Gang Qu</b> , University of Maryland                                  |                                         |  |

| 09:00-09:40                                                    | Prof. Tim Kwang-Ting CHENG, The Hong Kong University of Science                | Cinderella Ballroom                     |  |

|                                                                | and Technology                                                                 |                                         |  |

|                                                                | Speech Title: Design and EDA for Edge Inference Chips Supporting               |                                         |  |

|                                                                | Large-Scale Multi-Modal AI Models: The InnoHK ACCESS Approach                  |                                         |  |

| 09:40-10:20                                                    | Prof. Sachin S. Sapatnekar, University of Minnesota                            |                                         |  |

| 05.40 10.20                                                    | Speech Title: Automating Analog Design for the 21st Century                    |                                         |  |

| 10:20-10:40                                                    | Break                                                                          | Foyer                                   |  |

|                                                                | Technical Session 23                                                           | Sleeping Beauty 1/2                     |  |

|                                                                | Advanced Timing Analysis and Optimization                                      | Sleeping beauty 1/2                     |  |

|                                                                | Technical Session 24                                                           | Sleeping Beauty 3                       |  |

|                                                                | System-Level Design Exploration and NoC Innovations                            | Sleeping beauty 5                       |  |

| 10:40-12:00                                                    | Technical Session 25                                                           | Snow White 2/3                          |  |

| 10.40-12.00                                                    | RTL and Gate-Level Simulation and Verification                                 | 311011 11111111111111111111111111111111 |  |

|                                                                | Technical Session 26                                                           | Snow White 1                            |  |

|                                                                | Packaging, Chiplet Design, and Multi-Physics Simulation                        |                                         |  |

|                                                                | Technical Session 27                                                           | Sleeping Beauty 5                       |  |

|                                                                | Advanced Simulation and Optimization in Semiconductor Processes                | 1 3 9                                   |  |

| 12:00-14:00                                                    | Lunch & Keynote Speeches                                                       |                                         |  |

|                                                                | Keynote Speech 9 & 10                                                          |                                         |  |

| Host: <b>Tsung-Yi Ho</b> , The Chinese University of Hong Kong |                                                                                |                                         |  |

| 12:30-13:10                                                    | Prof. Jaijeet Roychowdhury, University of California, Berkeley                 | Cinderella Ballroom                     |  |

|                                                                | Speech Title: Oscillator Ising Machines: Principles and Design                 |                                         |  |

|                                                                | Assoc. Prof. Vijay Janapa Reddi, Harvard University                            |                                         |  |

| 13:10-13:50                                                    | <b>Speech Title</b> : Architecture 2.0: Foundations of Artificial Intelligence |                                         |  |

|                                                                | Agents for Modern Computer System Design                                       |                                         |  |

#### May 12, 2025 | Monday

09:00-09:40 | May 10, 2025 @ Cinderella Ballroom

#### Giovanni De Micheli

École polytechnique fédérale de Lausanne (EPFL)

**Bio.:** Giovanni De Micheli is a research scientist in electronics and computer science. He is credited for the invention of the Network on Chip design automation paradigm and for the creation of algorithms and design tools for Electronic Design Automation (EDA). He is Professor and Director of the Integrated Systems Laboratory and Scientific Director of the EcoCloud center at EPFL Lausanne, Switzerland. Previously, he was Professor of Electrical Engineering at Stanford University. He was Director of the Electrical Engineering Institute at EPFL from 2008 to 2019 and program leader of the Swiss Federal Nano-Tera.ch program. He holds a Nuclear Engineer degree (Politecnico di Milano, 1979), a M.S. and a Ph.D. degree in Electrical Engineering and Computer Science (University of California at Berkeley, 1980 and 1983).

Prof. De Micheli is a Fellow of ACM, AAAS and IEEE, a member of the Academia Europaea and an International Honorary member of the American Academy of Arts and Sciences. His current research interests include several aspects of design technologies for integrated circuits and systems, such as synthesis for emerging technologies. He is also interested in heterogeneous platform design including electrical components and biosensors, as well as in data processing of biomedical information. He is author of: Synthesis and Optimization of Digital Circuits, McGraw-Hill, 1994, co-author and/or co-editor of ten other books and of over 900 technical publications. His citation h-index is above 100 according to Google Scholar. He is member of the Scientific Advisory Board of IMEC (Leuven, B) and STMicroelectronics.

Prof. De Micheli is the recipient of the 2022 ESDA-IEEE/CEDA Phil Kaufman Award, the 2019 ACM/SIGDA Pioneering Achievement Award, and several other awards.

#### **Title: The Future of Computing Systems Design**

**Abstract:** Increasingly more stringent requirements for computing systems will outpace our ability to design them using current technologies and methods. Fortunately, we can leverage design automation tools to analyze and synthesize new generations of computing machines, that will depart from their ancestors in terms of realization technology, computing paradigm and interaction with humans. Devices and chips technologies are already evolving into a third dimension. New materials are both enhancing silicon technology and creating viable alternatives. Accelerators of computation leverage the diversity of underlying technology. Yet their efficient design requires new design automation tools.

Within this plurality of possibilities, the computational intractability of even simple design problems will challenge our goals to achieve both high-performance and low-energy computing. Interestingly, many disparate design problems share kernel subproblems, that can be tackled with the help of graph models and discrete mathematics tools. Synthesis is and will be the key enabler for the progress in computing as well as for addressing efficient ways for enhancing privacy and security.

09:40-10:20 | May 10, 2025 @ Cinderella Ballroom

#### **Georges Gielen**

Katholieke Universiteit Leuven (KU Leuven)

**Bio.:** Georges G.E. Gielen received the MSc and PhD degrees in Electrical Engineering from the Katholieke Universiteit Leuven (KU Leuven), Belgium, in 1986 and 1990, respectively. Currently, he is Full Professor in the MICAS research division at the Department of Electrical Engineering (ESAT) at KU Leuven. From August 2013 until July 2017 he served as Vice-Rector for the Group of Sciences, Engineering and Technology. In 2018 he was visiting professor at UC Berkeley and Stanford University. From 2020 to 2024 he served as Chair of the Department of Electrical Engineering (ESAT) at KU Leuven.

His research interests are in the design of analog and mixed-signal integrated circuits, and especially in analog and mixed-signal CAD tools and design automation, including modeling, simulation, optimization and synthesis as well as testing.

He is a frequently invited speaker/lecturer and coordinator/partner of several (industrial) research projects in this area, including an ERC Advanced Grant. He has (co-)authored 10 books and more than 700 publications in edited books, international journals and conference proceedings. He is a 1997 Laureate of the Belgian Royal Academy of Sciences, Literature and Arts in the discipline of Engineering. He is Fellow of the IEEE since 2002, and received the IEEE CAS Mac Van Valkenburg award in 2015 and the IEEE CAS Charles Desoer award in 2020, as well as the EDAA Achievement Award in 2021. He is an elected member of the Royal Flemish Academy of Belgium in the class of Technical Sciences, and of the Academia Europaea.

Title: DeepDesignAMS: Will Tomorrow's Analog Integrated Circuits be Generated by AI?

**Abstract:** Analog/mixed-signal integrated circuits are key in applications where electronics interface with the physical world. But whereas digital circuits are largely synthesized through EDA software, surprisingly, the design of analog circuits in industry is mainly still handcrafted, with long and error-prone design cycles and high development costs. The recent rebirth of AI and machine learning, and the recent rise of generative AI methods, however, create a whole new spectrum of techniques to automate this process. This keynote presentation will explore the high potential of using advanced machine learning (ML) techniques to automatically synthesize and lay out analog integrated circuits. What is hype and what will be feasible? Will we still need analog designers in the future and how will they operate?

12:40-13:20 | May 10, 2025 @ Cinderella Ballroom

#### **Hong Zhou**

Institute of Strategic Research, Huawei

**Bio.:** Dr. Zhou, President of Huawei's Institute of Strategic Research, joined Huawei in 1997. Dr. Zhou has served as Chief of the Shanghai Research Center, Vice President of the Wireless Network Product Line, President of the Central Hardware Engineering Institute, and President of the European Research Institute etc. In these roles, Dr. Zhou has been responsible for research, standardization, industrialization, and technical cooperation activities of the related business.

Title: Building a Better Connected and Intelligent World with STCO Collaborative Development

**Abstract:** With the rapid development of digitization, intelligence, and greenization, we are standing at an unprecedented node in the era where society and economy, science and technology, culture and education will undergo tremendous changes in the future. This presents both new opportunities and unprecedented challenges for the ICT field, requiring industry and academia to jointly explore future oriented business visions and technological assumptions, from What to Why and How, to develop efficient, and creative intelligence, and build a better connected and intelligent world with STCO Collaborative Development.

#### 09:00-09:40 | May 11, 2025 @ Cinderella Ballroom

#### Sung Kyu Lim

Georgia Institute of Technology (Gatech)

**Bio.:** Prof. Sung Kyu Lim earned his Ph.D. in Computer Science from UCLA in 2000. Since 2001, he has been a faculty member at the School of Electrical and Computer Engineering at the Georgia Institute of Technology. His research explores the architecture, design, and electronic design automation (EDA) of 2.5D and 3D integrated circuits, contributing to over 400 published papers. He received the Best Paper Awards from the IEEE Transactions on CAD in 2022 and the ACM Design Automation Conference in 2023. He is an IEEE Fellow and served as a program manager at DARPA's Microsystems Technology Office from 2022 to 2024.

Speech Title: Enhancing AI Chip Design: AI and Traditional Algorithms for Multi-Chip Integration

**Abstract:** Multi-chip integration has become standard practice in AI training and is increasingly adopted in edge learning applications. By utilizing 2.5D and 3D IC architectures through multi-chip integration, significant improvements can be made in energy efficiency and latency reduction during data transfers. Central to these advancements is the automation of design and simulation processes for heterogeneous AI chips, where sophisticated algorithms increasingly play a pivotal role, rather than manual human intervention. This transition is powered by advanced electronic design automation (EDA) tools. At Georgia Tech, my research team combines AI-driven and conventional algorithms to enhance EDA capabilities, tailored specifically for the development of state-of-the-art heterogeneous AI chips. In my talk, I will highlight these technological innovations and discuss the prevailing challenges in AI chip design and EDA.

09:40-10:20 | May 11, 2025 @ Cinderella Ballroom

#### **Ulf Schlichtmann**

Technical University of Munich (TUM)

**Bio.:** Professor Schlichtmann (b. 1964) explores design automation methodologies for complex (digital and analog) electronic circuits and systems. These often consist of billions of components and need to be designed using sophisticated optimization and analysis algorithms. In recent years, his research has increasingly addressed emerging technologies (photonics, microfluidic biochips, neuromorphic architectures).

Professor Schlichtmann studied electrical engineering at TUM and obtained his doctorate for a thesis on computer-aided design, and also pursued a postgraduate business degree during this time. He then worked for Siemens AG and Infineon Technologies AG in a number of technical, managerial and executive positions for about 10 years. In 2003, Professor Schlichtmann was appointed to a professorship at TUM. In addition to his research and teaching activities, he coordinates international study programs in both Munich and Singapore (TUM Asia). He furthermore serves as program director of the TUMCREATE research project in Singapore and is is a member of various advisory boards and of the acatech National Academy of Science and Engineering.

#### Title: Optical Networks-on-Chip: EDA for the Future of Interconnect

Abstract: Optical networks-on-chip (ONoC) is a next-generation interconnect architecture, e.g. for multiprocessor systems-on-chip (MPSoC). Compared to classic electrical NoCs, ONoC offers much higher bandwidth with wavelength-division multiplexing (WDM), which allows signals to travel through the same medium simultaneously with little interference by modulating them on different wavelengths. Among various types of ONoCs, Wavelength-Routed ONoC (WRONoC) is renowned for being exempt from communication protocols. Specifically, instead of dynamically constructing/destructing signal paths, optical signals are routed passively according to their wavelengths along designated signal paths fixed in the design phase. This way, WRONoC avoids the energy and latency overhead for arbitration and enables all-to-all simultaneous data transmission. This talk presents three design synthesis methodologies and the corresponding research projects conducted at TUM for application-specific WRONoC. In addition, this talk will highlight opportunities for bit-level parallelism maximization and allocation during and after design synthesis and the corresponding challenges that must be addressed, particularly for large-scale networks.

12:30-13:10| May 11, 2025 @ Cinderella Ballroom

#### **Jinjun Xiong**

University at Buffalo

**Bio.:** Dr. Jinjun Xiong is Empire Innovation Professor with the Department of Computer Science and Engineering at University at Buffalo (UB). He also serves as the Scientific Director for the National AI Institute for Exceptional Education, the AI lead for the IES Center for Early Literacy and Responsible AI, and Director for the SUNY-UB Institute for Artificial Intelligence and Data Science. Prior to that, he was a Senior Researcher and Program Director for AI and Hybrid Clouds Systems at the IBM Thomas J. Watson Research Center. He was the former co-founder and co-director for the IBM-Illinois Center for Cognitive Computing Systems Research (C3SR), the success of which in 5 years has led to the 10-year \$200M expansion of the center to the IBM-Illinois Discovery Accelerator Institute. His research interests are on across-stack AI systems research, including AI applications, algorithms, tooling and computer architectures. Many of his research results have been adopted in IBM's products and tools. He published more than 180 peer-reviewed papers in top AI conferences and systems conferences. His publication won 9 Best Paper Awards and 10 Nominations for Best Paper Awards. He also won top awards from various international competitions, including the championship award for the IEEE GraphChallenge on accelerating sparse neural networks in 2020, and the First Place Awards for the 2019 DAC Systems Design Contest on designing an object detection neural network for edge FPGA and GPU devices, respectively.

#### Title: A Reflection on Machine Learning for EDA: What are Possible Future Directions?

**Abstract:** The increasing power of deep learning-based machine learning (ML) techniques have started to erode many of the traditional equation-based physical modeling techniques, some of which are corner stone technologies for the development of electronic design automation (EDA) as an active area in the past decades. Since the inception of the new area of ML for EDA, there have always been controversies or doubts on the sensibility of such a formulation. Based on the speaker's years of research experience in both EDA and ML as two separate domains, he will reflect upon his personal learning in these two seemingly different areas, how the controversies may be reconciled, and how a cohesive view on the subject of ML for EDA can be formed. In doing so, the speaker would like to shed some lights on the future of ML for EDA, and what research challenges are ahead of the ML for the EDA research community.

09:00-09:40 | May 12, 2025 @ Cinderella Ballroom

#### **Tim Kwang-Ting CHENG**

The Hong Kong University of Science and Technology

**Bio.:** Professor Tim Cheng is Vice-President for Research and Development (VPRD) and Chair Professor jointly in the Department of Electronic & Computer Engineering (ECE) and Department of Computer Science & Engineering (CSE) at The Hong Kong University of Science and Technology (HKUST). His current research interests span the fields of AI chip design, electronic design automation (EDA), computer vision, and medical image analysis. He is now directing the InnoHK AI Chip Center for Emerging Smart Systems (ACCESS), a multidisciplinary R&D platform aiming to advance IC design and EDA development in realizing ubiquitous AI applications in society.

Prof. Cheng holds a doctorate from the Univ. of California, Berkeley. Prior to joining HKUST, he was on the faculty at the Univ. of California, Santa Barbara (UCSB) after spending five years at the AT&T Bell Laboratories. At UCSB, he took up various academic leadership roles, including the Founding Director of the Computer Engineering Program, Chair of the ECE Department, and Associate Vice Chancellor for Research. He was Dean of Engineering at HKUST from 2016 to April 2022 before becoming VPRD.

A Fellow of IEEE and the Hong Kong Academy of Engineering Sciences, Prof. Cheng has gained due recognition for his research, including a dozen of best paper awards from IEEE and ACM conferences and journals. On top of receiving the UCSB College of Engineering Outstanding Teaching Faculty Award, the 2020 Pan Wen Yuan Outstanding Research Award, and the 2024 CCF Overseas Outstanding Contribution Award, he was named a Fellow of the School of Engineering at the University of Tokyo.

Title: Design and EDA for Edge Inference Chips Supporting Large-Scale Multi-Modal AI Models: The InnoHK ACCESS Approach

**Abstract:** I will give an overview of the multi-faceted technical approaches and recent results at the InnoHK AI Chip Center for Emerging Smart Systems (ACCESS) research center in designing high-performance and energy-efficient edge accelerators for supporting inference of large-scale AI models. Four major trends are driving ACCESS's research agenda: (1) The growth rate of AI model size and complexity is much faster than the performance improvement rate of AI hardware, (2) latency, scalability, privacy, and reliability are driving migration of AI from cloud to edge, (3) AI model inference market is explosive, becoming much bigger than the model training market, and (4) chiplet/3DIC is going mainstream for AI processor implementation. I will showcase our approaches to design of Transformer and LLM accelerators, compute-in-memory macros, an application-algorithm-architecture co-design framework, and an automatically synthesized FPGA-based accelerator for convex optimization solvers.

09:40-10:20 | May 12, 2025 @ Cinderella Ballroom

#### Sachin S. Sapatnekar

University of Minnesota

**Bio.:** Sachin S. Sapatnekar is the Henle Chair in ECE and Distinguished McKnight University Professor at the University of Minnesota. His research interests include design automation methods for analog and digital circuits, circuit reliability, and algorithms and architectures for machine learning and quantum-inspired computing. He is a Fellow of the IEEE and the ACM.

#### **Title: Automating Analog Design for the 21st Century**

**Abstract:** Today's computing models see increasing analog content for two reasons: ever-increasing interaction with an analog real world, and the growing realization that computing on analog substrates can, under certain circumstances, be more efficient than traditional digital computing. For decades, automation has eluded analog design, but with growing design complexity, messy design rules and nontrivial constraints, there has been a renaissance in this field aided partially (but not exclusively) by the emergence of AI. The talk will first overview experience in analog design automation, particularly our experiences with the ALIGN layout automation system, and will overview directions for future research in the field.

#### 12:30-13:10 | May 12, 2025 @ Cinderella Ballroom

### Jaijeet Roychowdhury

University of California, Berkeley

**Bio.:** Jaijeet Roychowdhury is a Professor of EECS at the University of California at Berkeley. His research interests include machine learning, novel computational paradigms, and the analysis, simulation, verification and design of cyber-physical, electronic, biological, nanoscale and mixed-domain systems. Contributions his group has made include the concept of self-sustaining oscillators for Ising-based and von Neumann computation, novel machine-learning techniques for dynamical systems, theory and techniques for oscillator phase macromodels, injection locking and phase noise, multi-time partial differential equations, techniques for model reduction of time-varying and nonlinear systems, and open-source infrastructures for reproducible research.

Roychowdhury received a Bachelor's degree in electrical engineering from the Indian Institute of Technology, Kanpur, India, in 1987, and a Ph.D. degree in electrical engineering and computer science from UC Berkeley in 1993. From 1993 to 1995, he was with the Computer-Aided Design (CAD) Laboratory, AT&T Bell Laboratories, Allentown, PA. From 1995 to 2000, he was with the Communication Sciences Research Division, Bell Laboratories, Murray Hill, NJ. From 2000 to 2001, he was with CeLight Inc. (an optical networking startup), Silver Spring, MD. From 2001-2008, he was with the Electrical and Computer Engineering Department and the Digital Technology Center at the University of Minnesota in Minneapolis.

Roychowdhury was cited for Extraordinary Achievement by Bell Laboratories in 1996 for work on MOS

homotopy. His student Tianshi Wang and he won the Bell Labs Prize in 2019 for their work on Oscillator Ising Machines. Over the years, he has authored or co-authored seven best papers and a distinguished paper. He has served on technical and administrative committees within several conferences and professional organizations, including ICCAD, DAC, DATE, ASP-DAC and CEDA. Roychowdhury was a co-founder of Berkeley Design Automation, a startup later acquired by Mentor Graphics. He is a Fellow of the IEEE.

**Title: Oscillator Ising Machines: Principles and Design**

**Abstract:** Modern society has become increasingly reliant on rapid and routine solution of hard discrete optimization problems. Over the past decade, fascinating analog hardware approaches have arisen that combine principles of physics and computer science with optical, electronic and quantum engineering to solve combinatorial optimization problems in new ways---these have come to be known as Ising machines. Such approaches leverage analog dynamics and physics to find good solutions of discrete optimization problems, potentially with advantages over traditional algorithms. Underlying these approaches is the Ising model, a simple but powerful graph formulation with deep historical roots in physics.

About eight years ago, we discovered that networks of analog electronic oscillators can solve Ising problems "naturally". This talk will cover the principles and practical development of these oscillator Ising machines (OIMs). We will touch upon specialized EDA tools for oscillator based systems and note the role of novel nanodevices. Applied to the MU-MIMO detection problem in modern wireless communications, OIMs yield near-optimal symbol-error rates (SERs), improving over the industrial state of the art by 20x for some scenarios.

## **KEYNOTE SPEAKERS**

13:10-13:50 | May 12, 2025 @ Cinderella Ballroom

#### Vijay Janapa Reddi

Harvard University

Bio.: Vijay Janapa Reddi is an Associate Professor in the John A. Paulson School of Engineering and Applied Sciences at Harvard University. Prior to joining Harvard University, he was an Associate Professor at The University of Texas at Austin. His research interests include computer architecture and runtime systems, specifically in the context of edge and mobile computing systems (smartphones, autonomous vehicles, aerial robots, etc.) to improve their performance, power efficiency, and reliability. Dr. Janapa Reddi is a recipient of multiple honors and technical achievement awards, including the MICRO and HPCA Hall of Fame (2018 and 2019, respectively), the National Academy of Engineering (NAE) Gilbreth Lecturship Honor (2016), IEEE TCCA Young Computer Architect Award (2016), Intel Early Career Award (2013), Google Faculty Research Awards (2012, 2013, 2015, 2017), Best Paper at the 2005 International Symposium on Microarchitecture (MICRO), Best Paper at the 2009 International Symposium on High Performance Computer Architecture (HPCA), and IEEE's Top Picks in Computer Architecture awards (2006, 2010, 2011, 2016, 2017). Beyond his technical research contributions, Dr. Janapa Reddi is passionate about STEM education at early age. He is responsible for the Austin Independent School District's "hands-on" computer science (HaCS) program, which teaches 6th- and 7th-grade students programming and the high-level principles governing a computing system using open-source prototyping platforms like Arudinos. He received a BS in computer engineering from Santa Clara University, an MS in electrical and computer engineering from the University of Colorado at Boulder, and a Ph.D. in computer science from Harvard University.

## Speech Title: Architecture 2.0: Foundations of Artificial Intelligence Agents for Modern Computer System Design

Abstract: Modern computing systems have reached unprecedented levels of complexity, rendering traditional design methodologies increasingly inadequate. As system architectures evolve toward greater specialization and heterogeneity, the challenge intensifies, particularly with the rise of domain-specific architectures that demand intricate optimization across multiple design parameters. This complexity explosion necessitates fundamentally new approaches to system design and optimization. Artificial intelligence agents have demonstrated transformative potential across diverse fields, from autonomous systems to scientific discovery, offering data-driven methodologies that can navigate complex decision spaces. These agents, powered by deep learning and reinforcement learning, have shown remarkable capabilities in domains requiring continuous adaptation and intelligent decision-making. The next frontier is to harness similar agent-based approaches for architectural design and optimization, potentially revolutionizing how we approach memory controller optimization, resource allocation, compiler tuning, and power management. While current ML-assisted architecture research has produced innovative algorithms and methods that enhance system efficiency through learned embeddings and automated design space exploration, the full potential of autonomous AI agents in system design remains largely untapped. As we stand at the threshold of "Architecture 2.0," a crucial guestion emerges: What foundational infrastructure must be established to enable AI agents to transform computer system design? This talk examines the essential building blocks for developing AI agent-assisted architecture research through a shared ecosystem. Such infrastructure would provide standardized environments for agent development, training datasets, and unified platforms for reproducible experimentation and comparative analysis. The talk presents a vision for collaborative ecosystem development that addresses the unique challenges of bringing AI agents to systems and architecture research. Through collective effort, we can establish the foundations to transform modern computer system design for the next generation of computing.

## **TUTORIALS**

#### **T01. Test and Health Monitoring under Approximations and Variations**

#### 14:00-17:00 | May 9, 2025 @ Snow White 1

**Abstract:** Process and dynamic variations including voltage and temperature fluctuations, crosstalk interaction or aging effects complicate distinguishing between defects, reliability threats, and benign behavior. New compute paradigms like approximate computing aggravate the problem since they may hide malicious reliability threats. This tutorial introduces into the most recent techniques for offline and online test and health monitoring under variations and presents simulation and test generation techniques to overcome the multi-dimensional variation space. Case studies show, how error rate monitoring under dynamic voltage/frequency scaling and approximate computing and communication lead to improvements of performance, power consumption and reliability at the same time.

#### Hans-Joachim Wunderlich

University of Stuttgart

**Bio.:** Hans-Joachim Wunderlich is Professor Emeritus of the University Stuttgart and a Life Fellow of IEEE. He received the diploma degree in mathematics from the University of Freiburg, Germany, in 1981 and the Dr. rer. nat. (Ph.D. degree) from the University of Karlsruhe in 1986. Since 1991, he has been a full professor. From 2002 to 2018, he was the director of the Institute of Computer Architecture and Computer Engineering at the University of Stuttgart, Germany. He has been associate editor of various international journals and organizer of a variety of IEEE conferences on design, test and fault tolerance of electronic systems. He has published 15 books and book chapters and around 300 reviewed scientific papers in journals and conferences. His research interests include test, reliability, fault tolerance and design automation of microelectronic systems.

## **TUTORIALS**

#### **T02. Advanced Open-Source FPGA HLS and Physical Implementation Tools**

#### 14:00-17:00 | May 9, 2025 @ Cinderella 3

Organizers: Yibo Lin, Peking University; Zhi-Xiong Di, Southwest Jiaotong University

**Abstract:** Computer-Aided Design (CAD) of Field-Programmable Gate Arrays (FPGAs) has been a hot topic in the rapid advancement and adoption of FPGA technology over the past decades. FPGA CAD flow consists of three major steps: high-level synthesis (HLS) and logic synthesis, physical implementation, and bitstream generation.

FPGA CAD flow has several unique characteristics different from conventional application specific integrated circuit (ASIC) design flows due to the high heterogeneity of FPGA architectures, for example, instance packing, resource heterogeneity and large routing scale. Thus, most of the existing works highly rely on FPGA vendors' CAD tools to obtain indirect feedback and tightly bind to vendors' architectures, limiting the flexibility of algorithms and the ability to adapt to new FPGA architectures.

In this tutorial, we have planned three talks to address different aspects of open-source FPGA CAD tools to tackle those challenges. Our first session will provide OpenPARF, an open-source placement and routing framework for large-scale heterogeneous FPGAs with deep learning toolkits. Our second talk will introduce LEAPS, a comprehensive, systematic, and adaptable multi-die FPGA placement algorithm for SLL minimization. Our third session will delve into novel power modeling and optimization strategies tailored for HLS, and introduce power-efficient design methodologies on modern heterogeneous reconfigurable platform, Versal ACAP.

#### **Zhi-Xiong Di**

Southwest Jiaotong University

**Bio.:** Zhi-Xiong Di, School of Integrated Circuits, Southwest Jiaotong University, Associate Professor, Doctoral Supervisor. His research focuses on physical implementation algorithms, FPGA accelerator design. He has published papers in IEEE TCAS-I, IEEE TCAS-II, IEEE TCAD, DAC, and others. He has served as a Guest Editor for IEEE TCAS-II, and has guided students to win first prizes multiple times in the EDA Elite Challenge.

#### Zhe Lin

Sun Yat-sen University

**Bio.:** Zhe Lin is an Assistant Professor at the School of Integrated Circuits, Sun Yat-sen University (SYSU). Before joining SYSU, he held research positions at Peng Cheng Laboratory, where he served as an Associate Research Fellow from January to March 2023 and as an Assistant Research Fellow from March 2020 to December 2021. He earned his Ph.D. in Electronic and Computer Engineering from the Hong Kong University of Science and

Technology (HKUST) in 2020. Dr. Lin was awarded the Huawei Young Academic Talent Funding and Oversea High-Caliber Personnel in Shenzhen. As the first author or corresponding author, his paper has been nominated for best paper awards at ICCD 2024, DATE 2022, and FCCM 2019. He served as a technical program committee member for several leading conferences, such as DAC 2025, DATE 2025, ASP-DAC 2025, and FPT 2024.

#### **Jiarui Wang**

Peking University

**Bio.:** Jiarui Wang is a fourth-year Ph.D. student at the School of Computer Science, Peking University, advised by Prof. Yibo Lin. He received the B.S. degree in Computer Science and Technology from Peking University in 2021. His research focuses are FPGA routing and multi-FPGA system design flows. He has published 11 papers in DAC, ASP-DAC, TCAD and others. He has served as a reviewer for TCAD and TODAES. He is the co-author of OpenPARF, a high-performance open-source FPGA placement and routing framework. He won the first prize of EDA Elite Challenge 2022.

#### Jing Mai

Peking University

**Bio.:** Jing Mai is a fourth-year Ph.D. student at the School of Computer Science, Peking University, under the supervision of assistant professor Yibo Lin. He received his bachelor's degree from the School of Information Science and Technology, Peking University in 2021. His research interests include machine learning-assisted electronic design automation, machine learning systems and high performance computing. He has published 13 papers in prestigious venues including DAC, ICCAD, ASP-DAC, ISPD, TCAD, TCAS-I, and TPDS. He is the core author of OpenPARF, a high-performance open-source FPGA placement and routing framework. He led a team to achieve second place in the MLCAD 2023 large-scale FPGA macro placement competition. He received the Best Paper Award at ISEDA 2024 and won First Place in the ACM SIGDA CADathlon Contest 2024.

## EDZ

## **TUTORIALS**

#### T03. VLSI Physical Design, From 2D to 3D

#### 14:00-17:00 | May 9, 2025 @ Cinderella 2

#### Organizer: Hailong Yao, University of Science and Technology Beijing

**Abstract:** VLSI physical design plays a pivotal role in the semiconductor industry. It serves as the crucial bridge between the conceptual design of integrated circuits and their actual fabrication, directly influencing the PPA (power, performance, area) and cost of the final chips. With the relentless pursuit of PPA in modern electronics, the significance of accurate and efficient physical design has become even more pronounced.

In recent years, there has been a remarkable evolution from traditional 2D ICs to 3D ICs. 2D ICs have long been the cornerstone of the semiconductor field, but as the limitations of planar scaling become increasingly evident, 3D IC technology has emerged as a promising alternative. 3D ICs stack multiple layers of active devices vertically, enabling shorter interconnect lengths, higher bandwidth, and better integration of heterogeneous technologies. This transition not only provides new opportunities for innovation, but also poses a series of new challenges in the physical design process.

This tutorial comprehensively covers the entire physical design process for both 2D and 3D ICs. It starts with an in-depth introduction to the fundamental concepts and basic algorithms in physical design, including different floorplanning strategies, placement and routing algorithms, clock tree synthesis methods, and timing analysis techniques. It also explores the latest research results in 3D IC physical design. By the end of this tutorial, attendees will have a solid understanding of the VLSI physical design process, and be acquainted with the challenges and opportunities in the research frontier for both 2D and 3D IC designs.

#### **Hailong Yao**

University of Science and Technology Beijing

Bio.: Hailong Yao is a second-level full professor at the School of Computer and Communication Engineering, University of Science and Technology Beijing. He received the Ph.D. degree in computer science and technology from Tsinghua University, Beijing, China, in 2007. From 2007 to 2009, he was a Postdoctoral Research Scholar with the Department of Computer Science and Engineering, University of California at San Diego, La Jolla, CA, USA. He served as Assistant and Associate Professor with the Department of Computer Science and Technology, Tsinghua University from 2009 to 2022. Since 2023, he has been a full Professor with the School of Computer and Communication Engineering, University of Science and Technology Beijing, Beijing, China. His research interests include computer-aided design for ASICs, chiplets, and microfluidic biochips. He has published over 100 academic papers in the EDA field, including more than 20 papers in the CCF-A class TCAD journal and DAC conference. He received several Best Paper Award (Nominations) at ICCAD, SASIMI, GLSVLSI, etc. He was awarded the First Prize for Wu Wenjun Artificial Intelligence Science and Technology Award (Technological Invention Award) in 2022 (the first accomplished person). He serves as the Chair of VLSI Physical Implementation Sub-committee in Ecosystem Development Accelerator of EDA (EDA2) (https://www.eda2.com/), Standing Committee Member of CCF VLSI Design committee. He serves as an

editorial board member of ACM Transactions on Design Automation of Electronic Systems (TODAES), and has served as TPC member of domestic and international conferences in the EDA field (such as DAC, ICCAD, DATE, ASPDAC, ISEDA, etc.) for more than 50 times. He is a senior Member of IEEE.

#### **Yuanqing Cheng**

Beihang University

**Bio.:** Yuanqing Cheng is a tenured associate professor of the School of Integrated Circuit and Engineering, Beihang University, Beijing, China. He received his Ph.D. degree from the Key Laboratory of Computer System and Architecture, Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China. After one year postdoc study at LIRMM, CNRS, France, he joined Beihang University. His research interests include design automation for 3D integrated circuits, as well as low power and architectural optimization of emerging semiconductor technologies. He is currently an editorial board member of Elsevier Integration, the VLSI journal, TPC member of ICCAD/DATE/ASP-DAC/ISEDA, the Treasury of IEEE CEDA Beijing Chapter and a senior member of the IEEE.

#### Hao Yan

Southeast University

**Bio.:** Hao Yan is an Associate Professor at the Southeast University. His research is focused on static timing analysis and optimization. In recent years, he has led projects such as the National Natural Science Fund for Young Scientists, National Key Research and Development Plan, and Provincial Key R&D projects. He has published over 30 papers in the field of Electronic Design Automation (EDA) at conferences such as IEEE/ACM DAC and ICCAD, and received a nomination for the Best Paper at ASP-DAC 2021. He has also guided students to win awards in the Integrated Circuit EDA Design Elite Challenge and the International Timing Analysis Competition (2021&2022 TAU Contest).

## **TUTORIALS**

#### T04. AHS: An EDA toolbox for Agile Chip Front-end Design

#### 14:00-17:00 | May 9, 2025 @ Sleeping Beauty 3

#### Organizer: Yun Liang, Peking University

Abstract: Compared to software design, hardware design is more expensive and time-consuming. This is partly because software community has developed a rich set of modern tools to help software programmers to get projects started and iterated easily and quickly. However, the tools are seriously antiquated and lacking for hardware design. Modern digital chips are still designed manually using hardware description language such as Verilog or VHDL, which requires low-level and tedious programming, debugging, and tuning. In this tutorial, we will introduce AHS: AHS: An EDA toolbox for Agile Chip Front-end Design, which covers new hardware design methodologies and various automation tools. From the design perspective, AHS presents different ways that use different programming interfaces and target different scenarios, including 1) a multi-level hardware intermediate representation based high-level synthesis flow, which uses C and C++ as the programming language; 2) an embedded hardware description language, which uses Rust as the programming language. From the verification perspective, we will present agile simulation and debugging tools, which can check the functional and performance behaviors of the hardware. Hardware design determines the peak performance, while the actual performance is determined by the software. In the end, we will also present a compiler and instrumentation tool for the DNN accelerator.

#### Yun Liang

Peking University

**Bio.:** Prof Yun (Eric) Liang is currently an Endowed Boya Distinguished Professor in the School of Integrated Circuit and EECS at Peking University. His research interest is at the hardware-software interface with work spanning electronic design automation (EDA), hardware and software co-design, and reconfigurable computing. He has authored over 100 scientific publications in the leading international journals and conferences. His research has been recognized with three Best Paper Awards and six Best Paper Award Nominations. He currently serves as Associate Editor of the ACM Transactions on Embedded Computing Systems (TECS) and ACM Transactions on Reconfigurable Technology and Systems (TRETS). He was the program chair of 30th Annual IEEE International Conference on Application-specific Systems, Architecture and Processors (ASAP) 2019 and the International Conference on Field Programmable Technology (FPT) 2022. He currently serves in the program committees in the premier conferences including DAC, ICCAD, FPGA, FCCM, HPCA, MICRO, ASPDAC, etc.

#### Jingwen Leng

Shanghai Jiao Tong University

**Bio.:** Jingwen Leng is a full professor at the Department of Computer Science and Engineering at Shanghai Jiao Tong University. His research direction is the intelligent computer system design for the artificial intelligence, with the focus on performance, energy efficiency, and reliability. He has received multiple grants from National Science Foundation of China and top industrial companies. He has published more than 50 papers in top tier computer architecture conferences and more than 10 domestic/international patents. His work has received best paper award or nomination at venues/conferences including IEEE Micro Top Picks, DAC, and PACT. He was also awarded the DAMO Young Fellow from Alibaba.

## EDA

## **TUTORIALS**

#### **T05. Formal Verification for EDA**

#### 14:00-17:00 | May 9, 2025 @ Sleeping Beauty 5

#### Organizer: Shaowei Cai, Institute of Software, Chinese Academy of Sciences

**Abstract:** In the realm of electronic design automation (EDA), the exponential growth in chip complexity-driven by advanced nodes, billions of transistors, and safety-critical applications-demands verification methodologies that transcend traditional simulation. While simulations validate observed scenarios, they cannot exhaustively check all possible states, leaving risks of undetected errors. Formal verification fills this gap, offering exhaustive analysis and becoming indispensable in modern IC development. Two pillars of formal verification-equivalence checking and model checking-play pivotal roles in ensuring functional integrity and reliability.

In this tutorial, we have planned two talks to introduce techniques of equivalence checking and model checking. Our first talk will introduce the fundamentals and recent advancements for constraint solving and combinatorial equivalence checking, with a particular interest in parallel algorithms, noting that constraint solving is the underlying engines for both equivalence checking and model checking. Following this, our second talk will provide an in-depth exploration of model checking, including fundamentals and challenges, as well as some prospects.

#### Shaowei Cai

Institute of Software, Chinese Academy of Sciences

**Bio.:** Shaowei Cai is a Professor at Institute of Software, Chinese Academy of Sciences. His research interests include constraint solving and formal verification. He has received the Best Paper Award at SAT 2021 and CP 2024 and Distinguished Paper Award at CAV 2024. He has won 10+ gold medals in SAT competitions, and won the Largest Leading Award and Largest Contribution Award 6 times in SMT Competitions, ranked 1st in more than 20 categories. He has led a team working on EDA formal verification tools, including equivalence checking and model checking. His solvers have been used in several EDA companies and also in software verification industries. The formal tools in his group have been used to successfully identify and fix bugs in XiangShan, which is a high-performance RISC-V multi-core processor.

#### **Hongce Zhang**

The Hong Kong University of Science and Technology (Guangzhou)

**Bio.:** Hongce Zhang is an Assistant Professor in Microelectronics Thrust at Hong Kong University of Science and Technology (Guangzhou). He received his PhD from Princeton University in 2021. He is a co-developer of the Pono model checker and his work on instruction-level abstraction (ILA) received the 2020 ACM TODAES best paper award. He has also served as the chair of IEEE Council on EDA, Guangzhou Chapter in 2023 and the program committee member for DAC, CAV, ICCD, FMCAD, GLSVLSI etc.

## **TUTORIALS**

#### **T06. LLM Applications in EDA**

#### 14:00-17:00 | May 9, 2025 @ Sleeping Beauty 1/2

Organizer: Fan Yang, Fudan University

#### Bei Yu

The Chinese University of Hong Kong

**Bio.:** Prof. Bei Yu is currently an Associate Professor in the Department of Computer Science and Engineering, The Chinese University of Hong Kong. He has served as TPC Chair of ACM/IEEE Workshop on Machine Learning for CAD, and in many journal editorial boards and conference committees. He received eleven Best Paper Awards from ICCAD 2024 & 2021 & 2013, IEEE TSM 2022, DATE 2022, ASPDAC 2021 & 2012, ICTAI 2019, the VLSI Journal in 2018, ISPD 2017, SPIE Advanced Lithography Conference 2016, and eight ICCAD/ISPD contest awards. He received IEEE CEDA Ernest S. Kuh Early Career Award in 2021, ACM SIGDA Meritorious Service Award in 2022, DAC Under-40 Innovator Award in 2024, and Hong Kong RGC Research Fellowship Scheme (RFS) Award in 2024.

#### Title: Large Language Model in EDA

**Abstract:** In this talk, we explore the burgeoning intersection of Large Language Models (LLMs) and Electronic Design Automation (EDA). We critically assess whether LLMs represent a transformative future for EDA or merely a fleeting mirage. By analyzing current advancements, challenges, and potential applications, we dissect how LLMs can revolutionize EDA processes like design, verification, and optimization. Furthermore, we contemplate the ethical implications and feasibility of integrating these models into EDA workflows. Ultimately, this talk aims to provide a comprehensive, evidence-based perspective on the role of LLMs in shaping the future of EDA.

#### **Ying Wang**

Institute of Computing Technology, Chinese Academy of Sciences

**Bio.:** Dr. Ying Wang is an professor in Institute of Computing Technology, Chinese Academy of Sciences, Beijing, and his current research interest includes the chip design automation, reliable computer architecture and memory system. He has published over 100 papers on IEEE/ACM conferences and journals, including TC, DAC, MICRO, HPCA and ICCAD. He has received several awards from international conferences, including the championship of IEEE LPIRC contest at DAC 2016, the championship of the System Design Contest at DAC 2018, 2024 IEEE Top Picks on IC testability and reliability, the Best Paper Award at ITC-Asia, GLSVLSI and ICCD. He is also the recipient of IEEE/ACM DAC under 40 innovator at 2021.

#### Title: Scaling Up the Hardware Design Capability of LLMs

**Abstract:** Hardware description language (HDL) code designing is a critical component of the chip design process, requiring substantial engineering and time resources. Recent advancements in large language models (LLMs), such as GPTs, have demonstrated their potential for automate this intricate task. Nevertheless, the